메모리 시스템과 캐시

오늘의 목표 : 메모리 시스템 이해하기!

1. 메모리 계층 구조 (Memory Hierarchy)

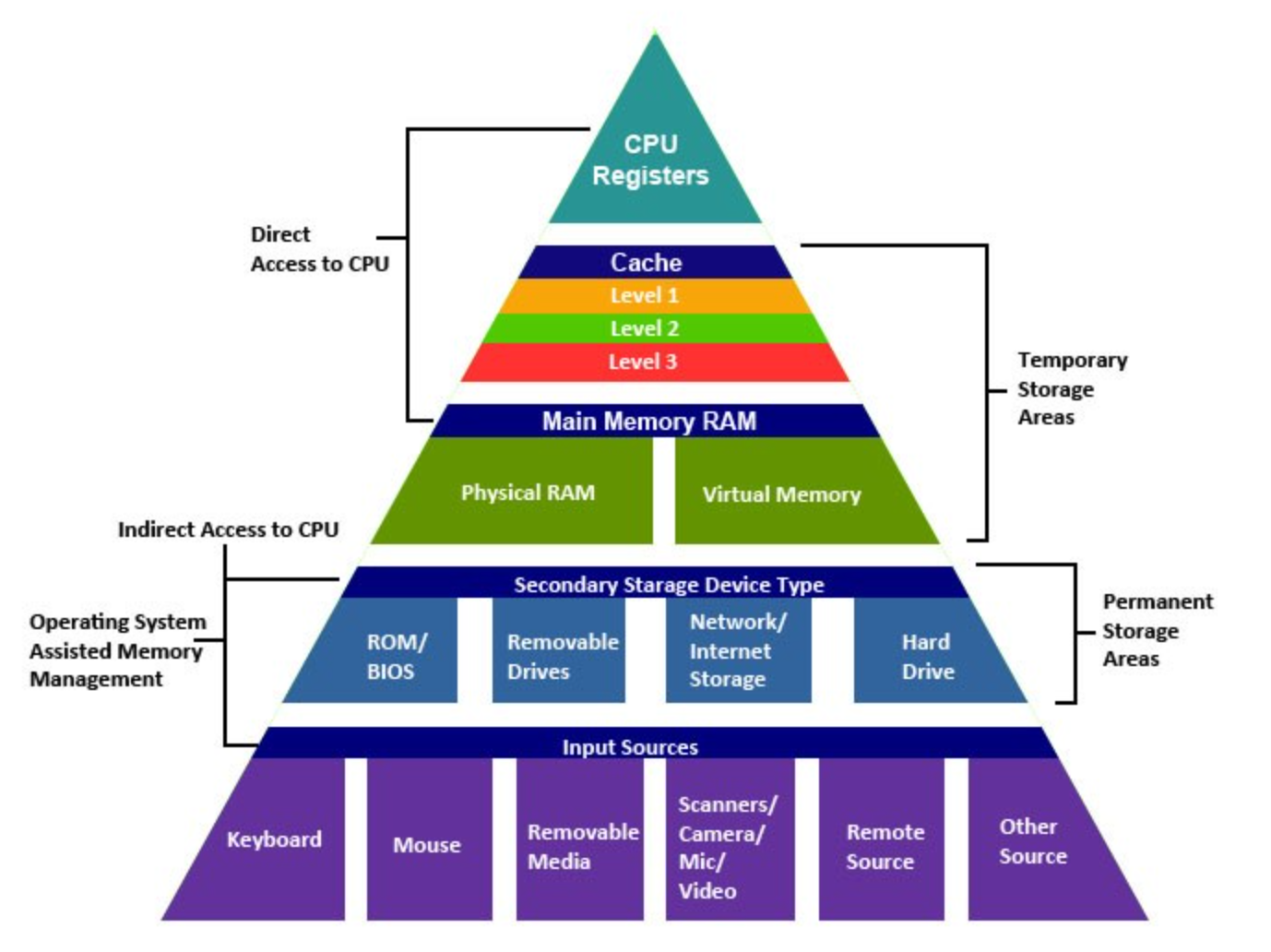

메모리 피라미드

(위 사진의 input sources는 안 다룰것이댜)

각 계층의 특징

레지스터 (Register)

- 용량: 32~64개 × 32/64비트 = 수백 바이트

- 속도: 1 클록 사이클

- 위치: CPU 내부

- 용도: 현재 작업 중인 데이터

L1 캐시 (Level 1 Cache)

- 용량: 16KB ~ 64KB

- 속도: 1-2 클록 사이클

- 위치: CPU 코어 내부

- 특징: 명령어 캐시(I-Cache)와 데이터 캐시(D-Cache)로 분리

L2 캐시 (Level 2 Cache)

- 용량: 256KB ~ 1MB

- 속도: 3-10 클록 사이클

- 위치: CPU 코어별 또는 공유

- 특징: 통합 캐시 (명령어 + 데이터)

L3 캐시 (Level 3 Cache)

- 용량: 8MB ~ 32MB

- 속도: 10-20 클록 사이클

- 위치: 여러 코어가 공유

- 특징: 코어 간 데이터 공유 역할

메인 메모리 (Main Memory, RAM)

- 용량: 4GB ~ 128GB

- 속도: 100-300 클록 사이클

- 기술: DDR4, DDR5

- 특징: 휘발성, 프로그램 실행 공간

보조기억장치 (Secondary Storage)

- SSD: 빠르지만 비쌈 (마이크로초 단위)

- HDD: 느리지만 저렴 (밀리초 단위)

- 특징: 비휘발성, 영구 저장

2. 캐시

캐시 메모리의 원리와 설계

캐시 정책

| 시간지역성 |

한 번 참조된 주소의 내용은 곧 다음에 다시 참조된다는 특성 |

|---|---|

| 공간지역성 |

한 번 참조한 메모리의 옆에 있는 메모리를 다시 참조하게 되는 성질 |

캐시의 기본 동작

- 캐시 히트 (Cache Hit)

CPU → 캐시 확인 → 데이터 있음! → 빠른 반환

(1-10 사이클)

- 캐시 미스 (Cache Miss)

CPU → 캐시 확인 → 데이터 없음 → 메인 메모리 접근 → 캐시 업데이트 → 반환

(100-300 사이클)

캐시 구조

- 캐시 라인 (Cache Line/Block)

- 캐시와 메모리 간 데이터 전송의 최소 단위

- 일반적으로 32바이트 ~ 128바이트

- 공간적 지역성 활용

- 태그 (Tag)

- 캐시 라인이 메모리의 어느 부분을 저장하고 있는지 식별

- 메모리 주소의 상위 비트들

- 유효 비트 (Valid Bit)

- 캐시 라인에 유효한 데이터가 있는지 표시

- 0: 무효, 1: 유효

- 캐시 교체 방식(정책)

- LRU (Least Recently Used)

- 가장 오래 사용되지 않은 블록을 교체

- FIFO (First In First Out)

- 가장 먼저 들어온 블록을 교체

- Random

- 무작위로 블록 선택

- LRU (Least Recently Used)

캐시 매핑 방식

- 직접매핑 : 메모리의 각 블록이 캐시의 정확히 한 위치에만 매핑

- 완전 연관 매핑 : 메모리의 어떤 블록이라도 캐시의 어느 위치에나 저장 가능

- 집합 연관 매핑 : 캐시를 여러 집합(set)으로 나누고, 각 집합 내에서는 완전 연관